**EEL4744**

EEL 4744C: µP Apps

## Menu

- Atmel XMEGA registers

- XMEGA Assembly Programming

- Addressing Modes for the XMEGA

- XMEGA Instruction Set

See examples on

web-site: [doc8331](#), [doc0856](#)

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

**EEL4744**

EEL 4744C: µP Apps

## XMEGA CPU General Purpose Working Register Summary

See [doc8331](#)

Fig 3-4

|                      | 7   | 0 | Addr. |

|----------------------|-----|---|-------|

|                      | R0  |   | 0x00  |

|                      | R1  |   | 0x01  |

|                      | R2  |   | 0x02  |

|                      | ... |   |       |

|                      | R13 |   | 0x0D  |

|                      | R14 |   | 0x0E  |

|                      | R15 |   | 0x0F  |

|                      | R16 |   | 0x10  |

|                      | R17 |   | 0x11  |

|                      | ... |   |       |

| X-register Low Byte  | R26 |   | 0x1A  |

| X-register High Byte | R27 |   | 0x1B  |

| Y-register Low Byte  | R28 |   | 0x1C  |

| Y-register High Byte | R29 |   | 0x1D  |

| Z-register Low Byte  | R30 |   | 0x1E  |

| Z-register High Byte | R31 |   | 0x1F  |

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

**EEL4744 XMEGA X, Y, Z Registers** See doc8331 Fig 3-5

**EEL 4744C: µP Apps**

- These registers can form 16-bit address pointers for addressing of the Data Memory.

- The Z-register can also be used as an address pointer to read/write to the Flash Program Memory, Fuses, Signature Rows, and Lock Bits.

|                      |                  |               |

|----------------------|------------------|---------------|

| 7<br>R27<br>XH<br>15 | 0 7<br>XL<br>8 7 | R26<br>0<br>0 |

| 7<br>R29<br>YH<br>15 | 0 7<br>YL<br>8 7 | R28<br>0<br>0 |

| 7<br>R31<br>ZH<br>15 | 0 7<br>ZL<br>8 7 | R30<br>0<br>0 |

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

3

3

**EEL4744 XMEGA Status Register** SREG called CPU\_SREG in Microchip (Atmel) Studio (SREG)

**EEL 4744C: µP Apps**

- Contains information about the result of the most recently executed arithmetic or logic instruction

|       |       |       |       |       |       |       |       |             |

|-------|-------|-------|-------|-------|-------|-------|-------|-------------|

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | <b>SREG</b> |

| +0x0F | I     | T     | H     | S     | V     | N     | Z     | C           |

| R/W-0       |

I = Global Interrupt Enable      Z = Zero Flag

T = Bit Copy Storage      See doc8331      C = Carry Flag

H = Half Carry Flag      Section 3.14.9

S = Sign Bit (S=N $\oplus$ V) [actual sign of result] (rarely used)

V = Two's Complement Overflow Flag

N = Negative Flag

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

4

4

**EEL4744 XMEGA Flags in SREG** See doc8331

Section 3.14.9

**Global Int Enable (I):** Set for interrupts to be enabled. If cleared, none of the interrupts are enabled. Can be set and cleared with the SEI and CLI instructions.

**Bit Copy Storage (T):** The instructions BLD and BST use the T bit as source or destination for the operated bit

**Half-Carry Flag (H):** Set if a carry occurs between bits 3 and 4 during some arithmetic instructions; otherwise, it is reset (to 0). Is useful in BCD arithmetic

**Sign Flag (S):**  $S = N \oplus V$ . The sign bit is the Exclusive-OR between the negative flag (N) and the two's complement overflow flag (V). **The actual sign of the result, even if there was an overflow.**

**Overflow (V):** Set if the last operation caused an arithmetic overflow; otherwise, it is reset. Ex: Set if the addition of two positive #'s (negative #'s) result in an apparently negative # (positive #).

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

**EEL4744 XMEGA Flags in SREG** See doc8331

Section 3.14.9

**Negative Flag (N):** Set if the result of the last arithmetic, logic, or data manipulation operation was negative; otherwise, it is reset

**Zero (Z):** Set if the result of the last arithmetic, logic, or data manipulation operation was zero; otherwise, it is reset

**Carry (C):** If an instruction operation results in a carry (from addition) or a borrow (from subtraction or comparison) out of bit 7 of the resulting value, then the Carry flag is set; otherwise, it is reset

**Key for Flags affected by Instructions**

|                                     |                       |

|-------------------------------------|-----------------------|

| ↔: Flag affected by instruction     | See doc0856<br>Page 7 |

| 0: Flag cleared by instruction      |                       |

| 1: Flag set by instruction          |                       |

| -: Flag not affected by instruction |                       |

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

EEL4744 XMEGA I/O Registers

**RAMPi** called **CPU\_RAMPi** in Microchip (Atmel) Studio, for  $i = X, Y, \text{ or } Z$

- **RAMPX, RAMPY, RAMPZ**

- > Registers concatenated with the X-, Y-, and Z-registers enabling indirect addressing of the whole data space on MCUs with more than 64K bytes data space, and constant data fetch on MCUs with more than 64K bytes program space.

- **Stack**

- > **STACK**: Stack for return address and pushed/popped registers

- > **SP**: Stack Pointer to STACK

**SP** called **CPU\_SPL** and **CPU\_SPH** in Microchip (Atmel) Studio

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

EEL4744 Special-Purpose Registers: PC & SP

- **Program Counter (PC):** A 16-bit register whose content addresses the memory location that contains the next instruction to be executed.

- **Stack Pointer (SP):** A 16-bit register which contains the address of the memory location in which the top of the stack is stored.

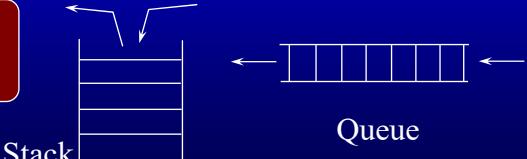

**Note:** Stack vs. Queue

LIFO      FIFO

Stack      Queue

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

EEL4744 Addressing Modes for XMEGA

EEL 4744C: µP Apps

- Direct Addressing Mode

- >Rd (destination) and Rr (source) Registers, JMP, CALL, examples: **LDS, STS**

- Indirect Addressing Mode

- >X, Y, Z Registers, IJMP, ICALL

- Extended Addressing Mode

- >EIJMP, EICALL

- Constant Addressing Mode

- >LPM, SPM - load/store program memory

- Relative Addressing Mode

- >RJMP and RCALL (PC = PC + k +1)

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

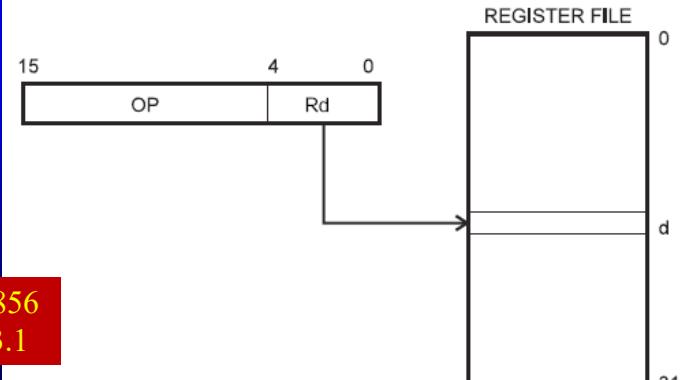

EEL4744 XMEGA Register Direct Addressing, Single Register

EEL 4744C: µP Apps

- Register Direct, Single Register Rd

- >Ex: **inc R16 ; R16 ← R16 + 1**

**See doc0856

Section 3.1**

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

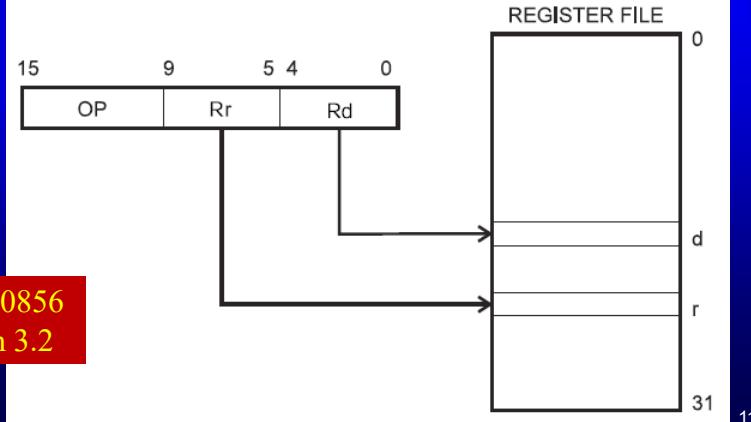

**EEL4744**      **XMEGA Register Direct Addressing, Two Registers**

- Register Direct, Two Registers Rd and Rr

- >Ex: **and R16, R17 ; R16 ← R16 AND R17**

REGISTER FILE

0      d      r      31

15      9      5 4      0

OP      Rr      Rd

See doc0856

Section 3.2

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

11

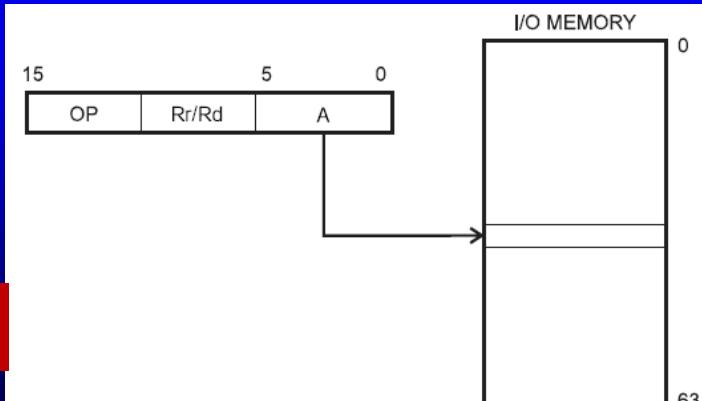

**EEL4744**      **XMEGA I/O Direct Addressing**

- I/O Direct Data Addressing **Addressing**

- >Operand address is contained in 6 bits of the instruction

- >Ex: **out CPU\_RAMPZ, r16 ; sts** would also work

- >Only works for addresses 0-63 (6 bits)

- >Rd/Rr is the destination/source register

I/O MEMORY

0      63

15      5      0

OP      Rr/Rd      A

See doc0856

Section 3.3

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

12

**EEL4744 XMEGA Data Direct Addressing**

- Direct Data Addressing

- >A 16-bit Data Address is contained in the 16 bits of a 2-word instruction

- >Ex: **lds R16, Total** ; R16  $\leftarrow$  (Total), Total is a label in **data space**, e.g., 0x2000

- >Rd/Rr is the destination/source register

See doc0856 Section 3.4

For some instruction this is 21 and 20

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

13

**EEL4744 XMEGA Data Indirect Addressing**

- Data Indirect Addressing

- >Operand address is the contents of the X-, Y-, or the Z-register

- >Register Indirect Addressing is a subset of Data Indirect Addressing since the data space from 0 to 31 is the Register File

- >Ex: **ld R16, X** ; R16  $\leftarrow$  (X)

See doc0856 Section 3.5

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

14

**EEL4744 XMEGA Data Indirect Addressing with Pre-decrement**

- Data Indirect Addressing with Pre-decrement

- > The X-, Y-, or the Z-register is decremented before the operation

- > Operand address is the decremented contents of the X-, Y-, or the Z-register

- > Ex: **st -Z, R16 ; Z ← Z-1, (Z) ← R16**

See doc0856

Section 3.6

15 0

X, Y OR Z - REGISTER

RAMEND 15

Data Space 0x0000

University of Florida, EEL 4744

© Drs. Schwartz & Arroyo

15

**EEL4744 XMEGA Data Indirect Addressing with Post-increment**

- Data Indirect Addressing with Post-increment

- > The X-, Y-, or the Z-register is incremented after the operation

- > Operand address is the content of the X-, Y-, or the Z-register prior to incrementing

- > Ex: **ld R16, Z+ ; R16 ← (Z), Z ← Z+1**

See doc0856

Section 3.7

15 0

X, Y OR Z - REGISTER

RAMEND 16

Data Space 0x0000

University of Florida, EEL 4744

© Drs. Schwartz & Arroyo

16

**EEL4744 XMEGA Data Indirect with Displacement Addressing**

- Data Indirect with Displacement

- > Operand address is the result of the Y- or Z-register contents added to the address contained in 6 bits of the instruction word

- > Ex: **ldd R16, Y+37 ; R16 ← (Y+37)**

- > Rd/Rr is the destination/source register

See doc0856

Section 3.8

University of Florida, EEL 4744C: µP Apps

© Drs. Schwartz & Arroyo

17

**EEL4744 XMEGA Program Memory Constant Addressing (LPM, SPM, ELP)**

- Program Memory Constant Addressing (LPM, SPM, ELP)

- > Constant byte address is specified by Z-register

- The 15 most significant bits (MSBs) select word address

- For LPM, selects low byte if LSB = 0; selects high byte if LSB = 1

- For SPM, the LSB should be cleared

- If ELP is used, the RAMZ Register is used to extend the Z-register

- > Ex: **lpm R16, Z ; R16 ← (Z)**

See doc0856

Section 3.9

University of Florida, EEL 4744C: µP Apps

© Drs. Schwartz & Arroyo

18

**EEL4744 XMEGA Program Memory with Post-increment (LPM Z+, ELPZ Z+)**

- Program Memory with Post-increment (w/ the LPM Z+ & ELPZ Z+)

- Constant byte address is specified by Z-register

- The 15 most significant bits (MSBs) select word address

- For LPM, selects low byte if LSB = 0; selects high byte if LSB = 1

- If ELPZ Z+ is used, the RAMPZ Register is used to extend the Z-register

**Ex: lpm R16, Z+ ; R16 ← (Z), Z ← Z+1**

See doc0856

Section 3.10

19

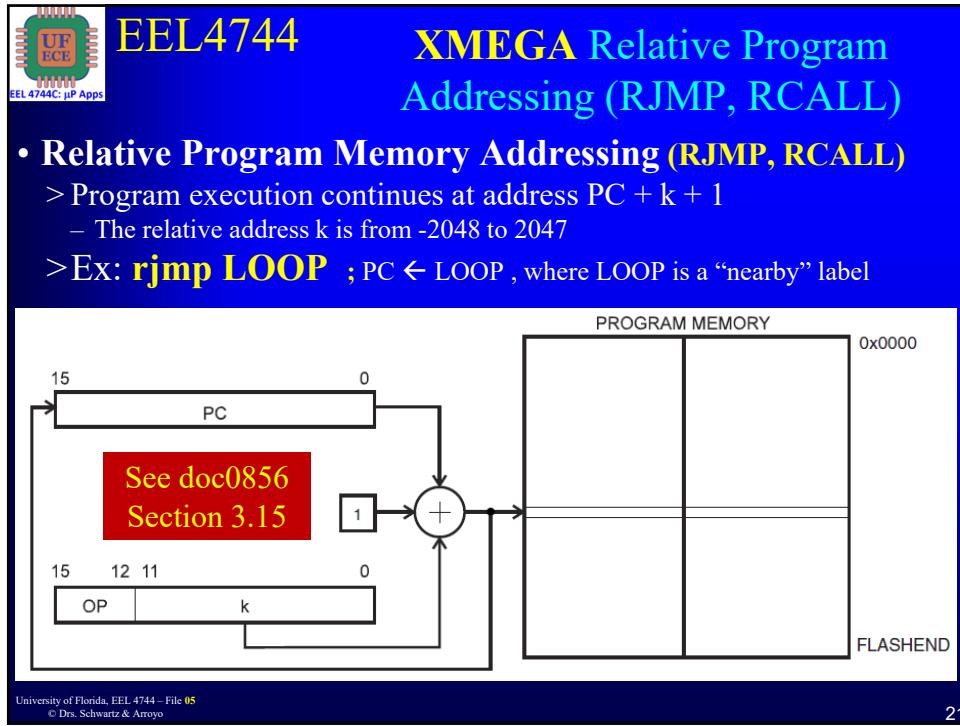

**EEL4744 XMEGA Direct Program Addressing (JMP, CALL)**

- Direct Program Memory Addressing (JMP, CALL)**

- Program execution continues at the immediate address in the instruction word

**Ex: jmp THERE ; PC ← THERE, where THERE is a label**

See doc0856

Section 3.12

20

21

21

The diagram shows the XMEGA conditional branch summary. It lists various conditional branches based on the state of the Z, N, and V flags. The table is as follows:

| Test         | Boolean                      | Mnemonic            | Complementary | Boolean                      | Mnemonic  | Comment  |

|--------------|------------------------------|---------------------|---------------|------------------------------|-----------|----------|

| $Rd > Rr$    | $Z \bullet (N \oplus V) = 0$ | BRLT <sup>(1)</sup> | $Rd \leq Rr$  | $Z + (N \oplus V) = 1$       | BRGE*     | Signed   |

| $Rd \geq Rr$ | $(N \oplus V) = 0$           | BRGE                | $Rd < Rr$     | $(N \oplus V) = 1$           | BRLT      | Signed   |

| $Rd = Rr$    | $Z = 1$                      | BREQ                | $Rd \neq Rr$  | $Z = 0$                      | BRNE      | Signed   |

| $Rd \leq Rr$ | $Z + (N \oplus V) = 1$       | BRGE <sup>(1)</sup> | $Rd > Rr$     | $Z \bullet (N \oplus V) = 0$ | BRLT*     | Signed   |

| $Rd < Rr$    | $(N \oplus V) = 1$           | BRLT                | $Rd \geq Rr$  | $(N \oplus V) = 0$           | BRGE      | Signed   |

| $Rd > Rr$    | $C + Z = 0$                  | BRLO <sup>(1)</sup> | $Rd \leq Rr$  | $C + Z = 1$                  | BRSH*     | Unsigned |

| $Rd \geq Rr$ | $C = 0$                      | BRSH/BRCC           | $Rd < Rr$     | $C = 1$                      | BRLO/BRCS | Unsigned |

| $Rd = Rr$    | $Z = 1$                      | BREQ                | $Rd \neq Rr$  | $Z = 0$                      | BRNE      | Unsigned |

| $Rd \leq Rr$ | $C + Z = 1$                  | BRSH <sup>(1)</sup> | $Rd > Rr$     | $C + Z = 0$                  | BRLO*     | Unsigned |

| $Rd < Rr$    | $C = 1$                      | BRLO/BRCS           | $Rd \geq Rr$  | $C = 0$                      | BRSH/BRCC | Unsigned |

| Carry        | $C = 1$                      | BRCS                | No carry      | $C = 0$                      | BRCC      | Simple   |

| Negative     | $N = 1$                      | BRMI                | Positive      | $N = 0$                      | BRPL      | Simple   |

| Overflow     | $V = 1$                      | BRVS                | No overflow   | $V = 0$                      | BRVC      | Simple   |

| Zero         | $Z = 1$                      | BREQ                | Not zero      | $Z = 0$                      | BRNE      | Simple   |

Note: 1. Interchange Rd and Rr in the operation before the test, i.e., CP Rd,Rr → CP Rr,Rd

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

22

EEL4744

## XMEGA Instructions: Arithmetic and Logic

- ADD, ADC, ADIW, SUB, SUBI, SBC, SBCI, SBIW

- AND, ANDI, OR, ORI, EOR, COM, NEG

- SBR (Set Bits in Register), CBR (Clear Bits in Register)

- INC, DEC

- TST (for 0 or negative)

- CLR (Clear Register), SER (Set Register)

- MUL, MULS, MULSU, FMUL, FMULS, FMULSU

- DES (Data Encryption)

Complete Instruction

Summary in doc0856

Section 4

EEL4744

## XMEGA Instructions: Branch Instructions

- See doc0856 page 10 (branch instructions, back 2 pages)

- > BREQ, BRNE, BRCS, BRCC, BRSH, BRLO, BRMI, BRPL

- > BRGE, BRLT, BRHS, BRHC, BRTS, BRTC, BRVS, BRVC

- > BRIE, BRID (Branch if Interrupt Enabled/Disabled)

- > BRBS, BRBS (Branch if Status Flag Set/Clear)

- **RJMP, IJMP, EIJMP, JMP**

- **RCALL, ICALL, EICALL, CALL**

- **RET, RETI**

- CPSE (ComPare, Skip if Equal), **CP, CPI**

- SBRC, SBRS (Skip if bit is Register is clr/set)

- SBIC, SBIS (Skip if bit is clr/set)

Complete Instruction

Summary in doc0856

Section 4

EEL4744

Skip if Bit ...

**sbrc Rr, b**

>This instruction tests a single bit in register Rr and skips the next instruction if the bit is cleared (0)

**sbrs Rr, b**

>This instruction tests a single bit in register Rr and skips the next instruction if the bit is set (1)

**cpse Rd, Rr**

>This instruction compares two registers and skips the next instruction if they are equal

EEL4744

## XMEGA Instructions: Data Transfer

- MOV, MOVW, LDI, **LDS**, LDD, LD (many)

- **STS**, ST (many)

- LPM, **ELPM (needed in Lab 1)** SPM, IN, OUT

- PUSH, POP (uses the stack)

- XCH

- LAS, LAC, LAT (Load and Set/Clear/Toggle)

• **lds** and **sts** are VERY useful

○ Example:

lds r16, 0x3744 ; r16 ← (0x3744)

Complete Instruction

Summary in doc0856

Section 4

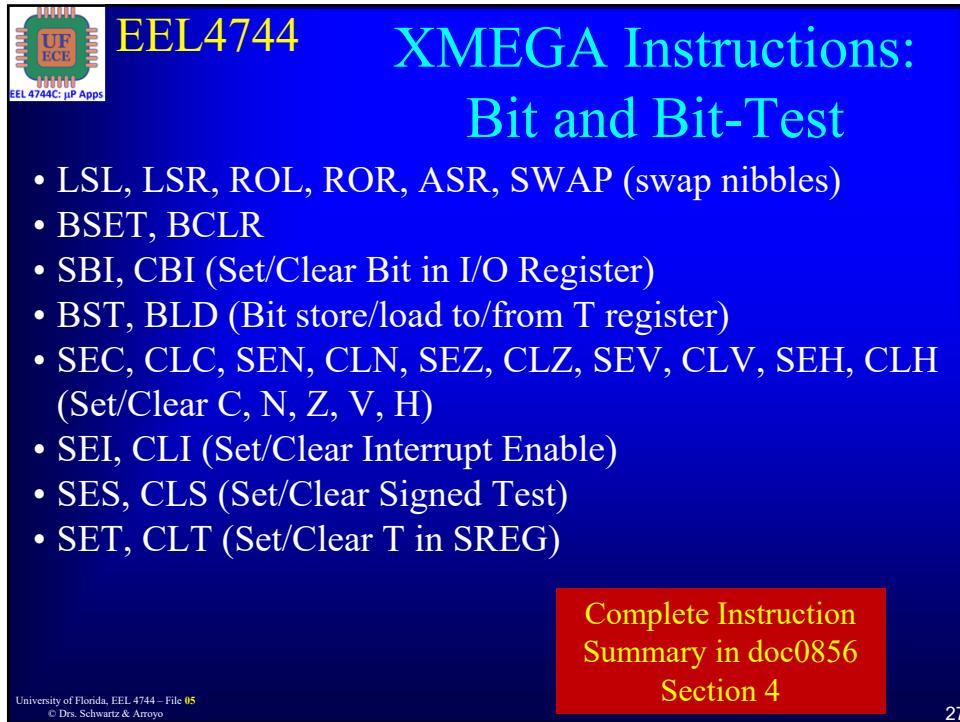

**EEL4744 XMEGA Instructions: Bit and Bit-Test**

- LSL, LSR, ROL, ROR, ASR, SWAP (swap nibbles)

- BSET, BCLR

- SBI, CBI (Set/Clear Bit in I/O Register)

- BST, BLD (Bit store/load to/from T register)

- SEC, CLC, SEN, CLN, SEZ, CLZ, SEV, CLV, SEH, CLH (Set/Clear C, N, Z, V, H)

- SEI, CLI (Set/Clear Interrupt Enable)

- SES, CLS (Set/Clear Signed Test)

- SET, CLT (Set/Clear T in SREG)

Complete Instruction Summary in doc0856

Section 4

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

27

**EEL4744**

## Using the T bit

**bst Rd, b**

>This instruction (**rarely used**) stores bit b from register Rd to the T Flag in SREG

**bld Rd, b**

>This instruction (**rarely used**) copies the T Flag bit in SREG to the bit b in register Rd

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

28

**EEL4744 XMEGA Instructions: MCU Control**

- BREAK, NOP, SLEEP, WDR (Watchdog Reset)

Complete Instruction Summary in doc0856

Section 4

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

29

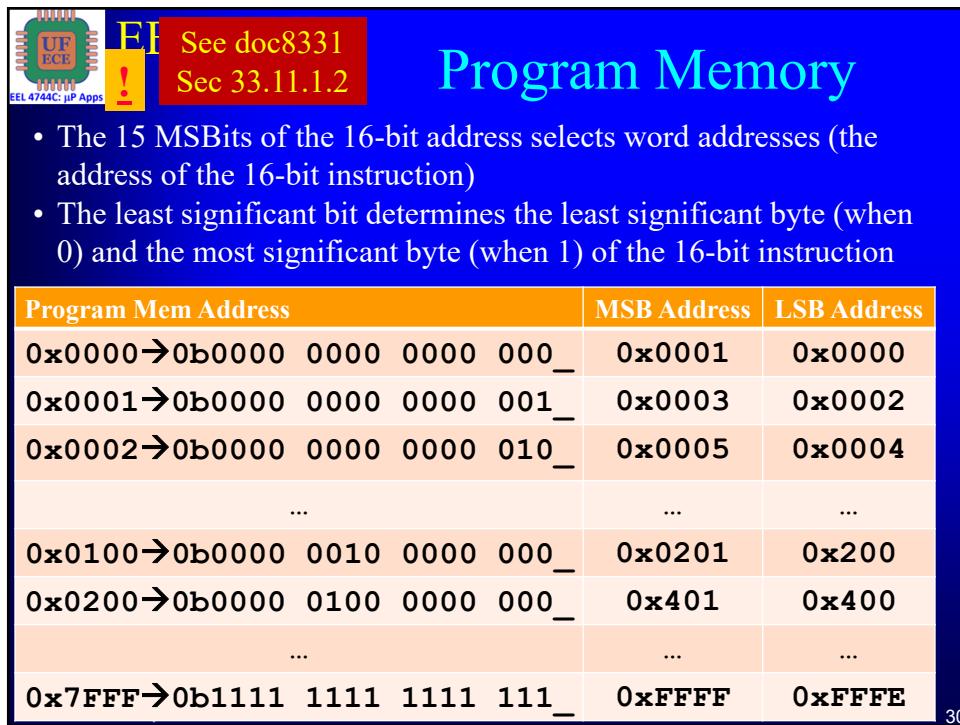

**Program Memory**

EI See doc8331

Sec 33.11.1.2

- The 15 MSBits of the 16-bit address selects word addresses (the address of the 16-bit instruction)

- The least significant bit determines the least significant byte (when 0) and the most significant byte (when 1) of the 16-bit instruction

| Program Mem Address            | MSB Address | LSB Address |

|--------------------------------|-------------|-------------|

| 0x0000 → 0b0000 0000 0000 000_ | 0x0001      | 0x0000      |

| 0x0001 → 0b0000 0000 0000 001_ | 0x0003      | 0x0002      |

| 0x0002 → 0b0000 0000 0000 010_ | 0x0005      | 0x0004      |

| ...                            | ...         | ...         |

| 0x0100 → 0b0000 0010 0000 000_ | 0x0201      | 0x200       |

| 0x0200 → 0b0000 0100 0000 000_ | 0x401       | 0x400       |

| ...                            | ...         | ...         |

| 0x7FFF → 0b1111 1111 1111 111_ | 0xFFFF      | 0xFFFF      |

30

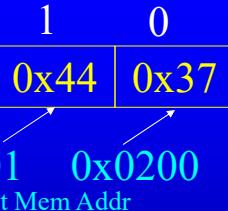

EEL4744

## 16-bit Versus 8-bit Data

Program (16-bit) Mem Addr 0x0100

8-bit Mem Addr 0x0201 0x0200

```

.cseg

.org 0x100

.db 0x37, 0x44

; get same result with below

.org 0x100

.dw 0x4437

```

- Program memory references 16-bit (word) numbers

- But with XMEGA, you can only access 8-bits at a time

- Apartment analogy

- > In Apartment 374, there are two rooms: 0 and 1

- > You can deliver mail to apartment 374 or to rooms 3740 and 3741

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

31

EEL4744

## Subroutine Control Instructions for XMEGA

- **call** (Call to Subroutine)

- > General format: **call** LABEL (or address)

- > Description: STACK  $\leftarrow$  PC+2

SP  $\leftarrow$  SP-2

PC  $\leftarrow$  k (constant address operand)

- **rcall** (Relative Call to Subroutine)

- > General format: **rcall** LABEL (or address)

- > Description: STACK  $\leftarrow$  PC+1

SP  $\leftarrow$  SP-2

PC  $\leftarrow$  PC+k+1 (constant address operand)

- **ret** (Return from Subroutine)

- > General format: **ret**

- > Description: PC  $\leftarrow$  STACK

SP  $\leftarrow$  SP+2

For Subroutine Control Examples,

see Lecture 7:

*Program Structures*

University of Florida, EEL 4744 – File 05

© Drs. Schwartz & Arroyo

32